Letters given out so far are the following.

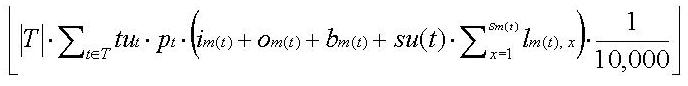

The scaling factor 1/10,000 is used to shorten the (often large) SOC test

complexity number obtained from the formula, in order to make it easier to use.

This page describes the benchmark format in detail. First, we explain how a

multi-level design hierarchy is expressed in the benchmark format.

Subsequently, we give a short description of all keywords used in the benchmark

format. Finally, we illustrate the format by means of an example SOC.

A uniform description of the SOC hierarchy is enabled by using the term

'Module' to denote each SOC component that is tested as a stand-alone unit. The

SOC itself, i.e., the top-level design unit, is a module. It contains the

non-core circuitry. Other modules are embedded in this top-level model. These

modules can be pre-designed embedded cores, but also user-defined modules, of

which the circuit structure and/or size justify stand-alone testing. And these

modules can in their turn contain again other modules, etc.

In order to express the design hierarchy in the benchmark format, we use the

keywords Module and Level. Modules are numbered in sequence,

starting with 'Module 0', which always represents the top-level SOC

design. The levels are also numbered in sequence and indicate the level of a

particular module in the design hierarchy tree. 'Module 0' has by

definition 'Level 0', whereas a module embedded in a module of

'Level n' has 'Level n+1'.

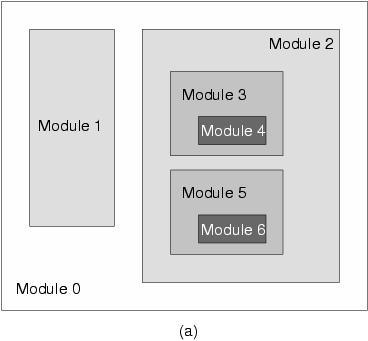

Figure 1(a) shows an example modular SOC design, containing seven modules. The

corresponding design hierarchy tree, consisting of four levels, is shown in

Figure 1(b).

For each module, the following information is specified.

Per test, the following is listed.

Line 04: Module 0 Level 0 Inputs 312 Outputs 312 Bidirs 0 ScanChains 2 : 54 43

Line 09: Module 1 Level 1 Inputs 10 Outputs 11 Bidirs 12 ScanChains 4 : 20 21 22 23

Line 15: Module 2 Level 1 Inputs 44 Outputs 46 Bidirs 0 ScanChains 1 : 100

Line 20: Module 3 Level 2 Inputs 312 Outputs 312 Bidirs 0 ScanChains 2 : 75 75

Line 24: Module 4 Level 3 Inputs 112 Outputs 543 Bidirs 23 ScanChains 0 :

Line 28: Module 5 Level 2 Inputs 312 Outputs 312 Bidirs 0 ScanChains 2 : 75 75

Line 32: Module 6 Level 3 Inputs 112 Outputs 543 Bidirs 23 ScanChains 0 :

The example x1331.soc has 35 lines with text and some blank lines. Please

note that the line numbers are not part of the format, but are added here for

explanation purposes only. The benchmark format allows to insert blank lines;

typically, this will be used to distinguish between the various module

descriptions.

The first three lines provide general information for this SOC. Line 1

says that the SOC name is 'x1331'. Line 2 specifies that the total number

of modules in this SOC is seven. Options in Line 3 lists whether

power and layout co-ordinate values for modules are supplied for this benchmark

SOC. Both options are listed as '1', which means that both X,Y

layout coordinates and power dissipation values are specified.

The next 33 lines describe the seven modules in the SOC. Lines 4-8

describe Module 0. Module 0 has Level 0, which means that

Module 0 is the top-level module. This is in fact always the case for

Module 0. Module 0 has 312 inputs, 312 outputs, and 0 bidirectional

terminals. It contains two scan chains, of lengths 54 and 43 scan flip flops,

respectively. Line 5 shows that no X,Y layout coordinates

are specified for Module 0. Module 0 has two tests. Test 1 uses

both its scan chains, as well as a TAM. The scan chains that are referred to

here are the two scan chains of Module 0 itself, as specified in

Line 4. Test 1 has 43 test patterns and dissipates 128 units of

power. Test 2 of Module 0 uses both its scan chains, as well as a

TAM. It has 32 test patterns and dissipates 537 units of power.

Lines 9-14 describe Module 1. Its level is 1, which means that

Module 1 is embedded within Module 0. Module 1 has 10 inputs, 11

outputs, and 12 bidirectional terminals. Module 1 has four scan chains, of

20, 21, 22, and 23 scan flip flops long respectively. The X co-ordinate is

given as 678 units and the Y co-ordinate is given as 123 units. Module 1

has three tests; all three use both the core-internal scan chains and a TAM.

Test 1 has 567 test patterns, and dissipates 576 units of power.

Test 2 has 876 test patterns, and dissipates 275 units of power.

Test 3 has 908 test patterns, and dissipates 123 units of power.

Modules 2 till 6 are described in the sequel of the example.

Modules 4 and 6 do not contain scan chains. Therefore, the parameter

ScanUse becomes irrelevant for their tests. The tests of these modules

also do not use a TAM, as their parameter TamUse is specified as '0'.

Modules 4 and 6 are probably non-logic cores that are tested by means of

an internal BIST.

From the order in which the modules of x1331 are specified and their level

information, we can establish that the design hierarchy of x1331 is as depicted

in Figure 1. Careful inspection of the example SOC shows that Module 3,

containing Module 4, has the same properties as Module 5, containing

Module 6. This might be due to the fact that Modules 3 and 5 are

equal, or, in other words, that Module 2 contains two instances of the

same core (although this is not guaranteed by the benchmark format).

Benchmark Naming

We have adopted a naming scheme for the benchmark SOCs with 'useful' benchmark

names. The names assigned to the benchmark SOCs consist of one letter, followed by a

number.

Letter

The letter represents the origin of the benchmark. Letters have been (and

continue to will be) given out to benchmark contributors on a

first-come-first-serve basis. This naming scheme is not guaranteed to be

conflict free, but we resolve name conflicts in an ad-hoc manner whenever they

occur. Three letters have a 'reserved meaning'.

Number

The subsequent number is a positive integer, meant to give an indication of the

test complexity of the SOC. The number is calculated based on a formula first

published in [Iyengar et al. - ITC'01]. Let T be the set of module

tests. For Test t in T and corresponding Module m(t), the

formula uses the numbers of primary inputs im(t), primary

outputs om(t), bidirectional terminals

bm(t), scan chains sm(t), internal scan

chain lengths lm(t),1, lm(t),2 , ...,

lm(t),sm(t), the binary parameters for

ScanUse sut and TamUse

tut, and the test pattern count pt. The

formula that calculates the SOC number is as follows.

Benchmark Format

The benchmark format contains the following information per SOC.

SOC Design Hierarchy

Our SOC benchmark format supports the description of multiple levels of design

hierarchy. We can describe the embedding of cores within cores. The format also

supports SOC design in which only some pre-designed cores are used, and the

remaining SOC circuitry is interconnect wiring, glue logic, and/or user-defined

blocks.

Keywords

The benchmark format uses keywords with the following meaning.

Example

We illustrate the benchmark format by means of an example SOC, named x1331.

x1331.soc

Line 01: SocName x1331

Line 02: TotalModules 7

Line 03: Options Power 1 XY 1

Line 05: Module 0 X -1 Y -1

Line 06: Module 0 TotalTests 2

Line 07: Module 0 Test 1 ScanUse 1 TamUse 1 Patterns 43 Power 128

Line 08: Module 0 Test 2 ScanUse 1 TamUse 1 Patterns 32 Power 537

Line 10: Module 1 X 678 Y 123

Line 11: Module 1 TotalTests 3

Line 12: Module 1 Test 1 ScanUse 1 TamUse 1 Patterns 567 Power 576

Line 13: Module 1 Test 2 ScanUse 1 TamUse 1 Patterns 876 Power 275

Line 14: Module 1 Test 3 ScanUse 1 TamUse 1 Patterns 908 Power 123

Line 16: Module 2 X 324 Y 98

Line 17: Module 2 TotalTests 2

Line 18: Module 2 Test 1 ScanUse 1 TamUse 1 Patterns 4356 Power 1334

Line 19: Module 2 Test 2 ScanUse 1 TamUse 1 Patterns 56 Power 2245

Line 21: Module 3 X 304 Y 80

Line 22: Module 3 TotalTests 1

Line 23: Module 3 Test 1 ScanUse 1 TamUse 1 Patterns 25 Power -1

Line 25: Module 4 X -1 Y -1

Line 26: Module 4 TotalTests 1

Line 27: Module 4 Test 1 ScanUse 1 TamUse 0 Patterns 12 Power -1

Line 29: Module 5 X 344 Y 80

Line 30: Module 5 TotalTests 1

Line 31: Module 5 Test 1 ScanUse 1 TamUse 1 Patterns 25 Power -1

Line 33: Module 6 X -1 Y -1

Line 34: Module 6 TotalTests 1

Line 35: Module 6 Test 1 ScanUse 1 TamUse 0 Patterns 12 Power -1

Erik Jan Marinissen, Vikram Iyengar, Krishnendu Chakrabarty - June 25, 2002